EDGECORTIX PRESS RELEASE

EDGECORTIX、業界をリードする低レイテンシと 高エネルギー効率を実現するSAKURA-I AI コプロセッサを発表

2022年4月22日、ソフトウェアファーストのアプローチで、エッジAI推論用の業界最高クラスの計算効率と低レイテンシを実現することに焦点を当てた革新的なファブレス半導体設計会社であるEdgeCortix® Inc.(本社:東京都渋谷区)は、業界を牽引する高効率の新しいAI推論コプロセッサのアーキテクチャ、性能指標および提供時期を発表しました。

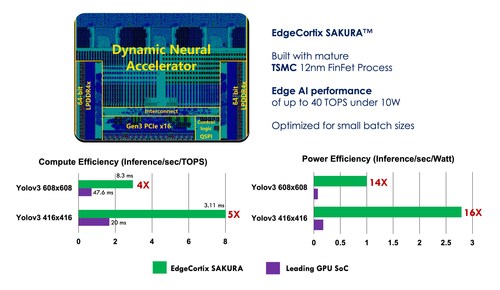

図:EdgeCortix SAKURA-Iチップダイの写真と、Yolov3オブジェクト検出ベンチマークでのエッジユースケースの主要なGPUとのAI推論効率の比較。 現在の主要なGPU SoCが、32 TOPSおよび30W TDPであるのに対し、EdgeCortix SAKURA-Iは40 TOPSおよび10W TDPです。SAKURA-Iは10倍以上の電力効率を実現します。すべてのデータは、Yolov3 608x608のベースラインに正規化され、バッチサイズは1です

EdgeCortixは本日、TechInsights社のLinley Spring Processor Conferenceにおいて、エネルギー効率に優れたAIコプロセッサ(アクセラレータ)であるフラッグシップブランド「SAKURA-I™」を正式に発表しました。 東京にある同社の開発センターで設計されたSAKURA-Iは、人気の高いTSMCの12nm FinFET技術によって製造され、省電力なPCI-Eベースの開発ボードとして、2022年7月にEdgeCortix Early Access Program (EAP)の参加企業に提供されます。

EdgeCortixの創設者兼CEOであるサキャシンガ・ダスグプタは次のように述べています。

「SAKURA-Iは、技術面から見ても、競争面からみても革新的で、特にリアルタイムのエッジアプリケーション用の従来のGPUをベースとしたAI推論ソリューションと比較すると、10倍以上のワットパフォーマンスを実現します。生産過程において、AIプロセッサアーキテクチャの設計を複数のFPGA顧客企業で検証した後、AI推論を大幅に高速化するための、ほぼ全ての既存システムのホストプロセッサに接続できるコプロセッサとしてSAKURA-Iを設計しました。当社の特許であるランタイムで再構成可能なインターコネクト技術を用いたSAKURA-Iは、従来のプロセッサと比較すると本質的に柔軟であり、過去40年以上にわたって開発された多くのAIプロセッサとは対称的に、最適なコンピューティング使用率を達成することが可能です。」

SAKURA-Iは、40TOPSのシングルコアであるDynamic Neural Accelerator® (DNA)IPを搭載しています。これは全ての計算エンジンをつなぐ再構成可能なデータパスを内蔵した当社の独自のニューラルプロセッシングエンジンです。DNAは新製品であるSAKURA-I AIコプロセッサにおいて、優れたTOPSを維持しながら、超低レイテンシで複数のディープニューラルモデルを実行することが可能です。この独自の特性は、SoCの処理速度、エネルギー効率、寿命を強化するカギとなり、TCO(総保有コスト)においても大きな利益をもたらします。DNA IPは、特にストリーミングデータや高解像度データの推論に最適化されています。

SAKURA-Iの性能プロファイルが理想とする主な産業分野は、輸送/自動運転車、防衛、セキュリティ、5G通信、VR/AR、スマート製造、スマートシティ、スマートリテール、ロボット工学など、省電力かつ低レイテンシのAI推論を必要とするすべての市場です。

また、SAKURA-Iは、複数のハードウェアのフォームファクタで購入できるほか、基盤となるIP(DNA)は、独自に半導体を設計する顧客向けに、EdgeCortixのソフトウェアスタックと組み合わせて、IPライセンスとして提供することも可能であると発表しました。

SAKURA-Iの主な特徴:

- 最大40TOPS (シングルチップ) / 200TOPS(マルチチップ)

- PCI-eデバイスのTDP @10W~15W

- 代表的なモデルの消費電力 ~5W

- 2x64 LPDDR4x – 16 GB

- PCIe Gen 3 – 最大16 GB/s の帯域幅

- 2つのフォームファクタ – デュアルM.2 / ロープロファイルPCIe

SAKURA-Iを搭載したDNAプロセッシングエンジンが実現すること:

- シングルコアで+24K MAC @ 800 MHz.

- INT8とバッチサイズ1に最適化

- ランタイムで再構成可能なデータパス

- 大容量オンチップメモリ– 20 MB

- ソフトウェアで定義された複数の並列度を利用することでコンピューティング使用率を最大化

- Yolov3やYolov5、ポイントクラウド処理ベースのAIなど、要求の厳しいワークロードで超低レイテンシ(4ms未満) を実現

また、EdgeCortixは、MERAコンパイラとソフトウェアフレームワークのオープンソース化を正式に公表し、同時に即日適用開始であることを発表しました。

MERAは、今日ますます複雑化し、計算量の多いAIワークロードをシームレスに高速化することで、ソフトウェアエンジニアがSAKURA-Iや、DNA IPを搭載した主要FPGA、その他のサードパーティーのシリコンをCPUやGPUのドロップイン代替品として使用できるようにします。

###

EdgeCortix株式会社について

EdgeCortixは、高効率なエッジインテリジェンスの実現に注力するファブレス半導体設計会社です。ハードウェアとソフトウェアを統合する「協調探索エンジン」という手法により、人工知能に特化したランタイムで再構成可能なプロセッサを一から設計しつつ、ソフトウェアファーストでアプローチするという考えのもと2019年7月に設立しました。高度なコンピュータビジョンアプリケーションをターゲットとし、FPGAやカスタムASIC設計などの既存のプロセッサ上でハードウェアやソフトウェアIPを使用して、防衛、航空宇宙、スマートシティ、インダストリー4.0、自律走行車、ロボット工学等、急速に成長しているAIハードウェア分野に積極的に参入することを目標としています。

詳細およびデモのご予約は下記までお願いします info@edgecortix.com

CONTACT:

EdgeCortix Newsroom

pr@edgecortix.com,

ph: +1415-818-0430

© Copyright 2022 EdgeCortix, Inc. All rights reserved worldwide. EdgeCortix、EdgeCortixのロゴおよび Dynamic Neural Accelerator は、EdgeCortix, Inc.およびそのグループ会社の日本およびその他の国における商標または登録商標です。また、その他の製品は全て各社の商標または登録商標です。

SOURCE Edgecortix, Inc.