Research and White Papers

Go in-depth with industry analysts and thought leaders on EdgeCortix products and technology in our Research and White Papers.

Sakura Debuts for Edge AI

Silicon Implementation Uses DNA IP for Low-Latency Inference

Linley Group Report: Software Is Critical to Edge-AI Deployment

The importance of a flexible and robust software stack to edge-AI deployment

Linley Group Report: EdgeCortix IP Lowers AI Latency

Startup’s High-End DNA IP Targets Level 3 ADAS

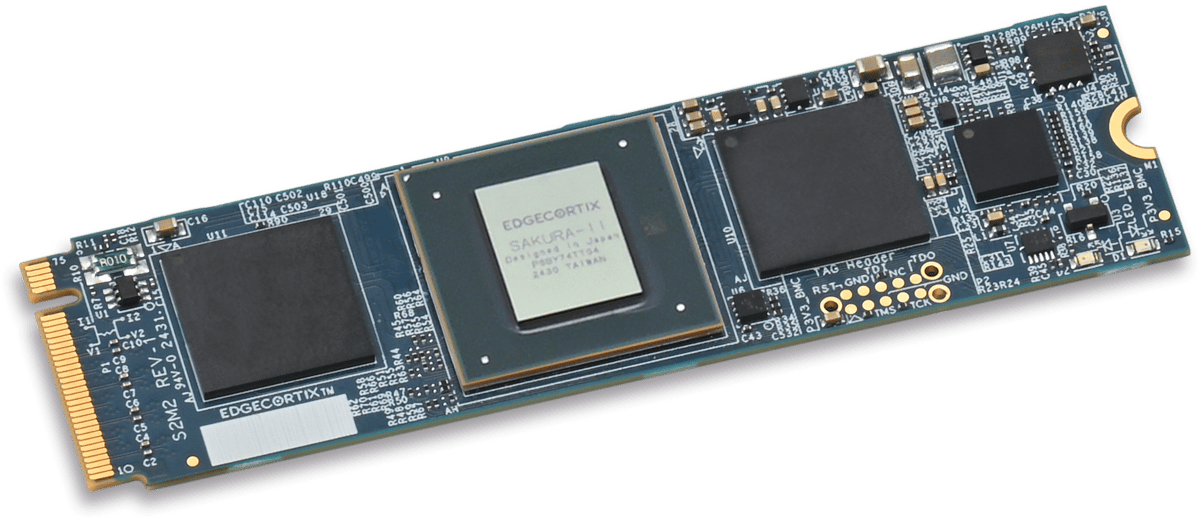

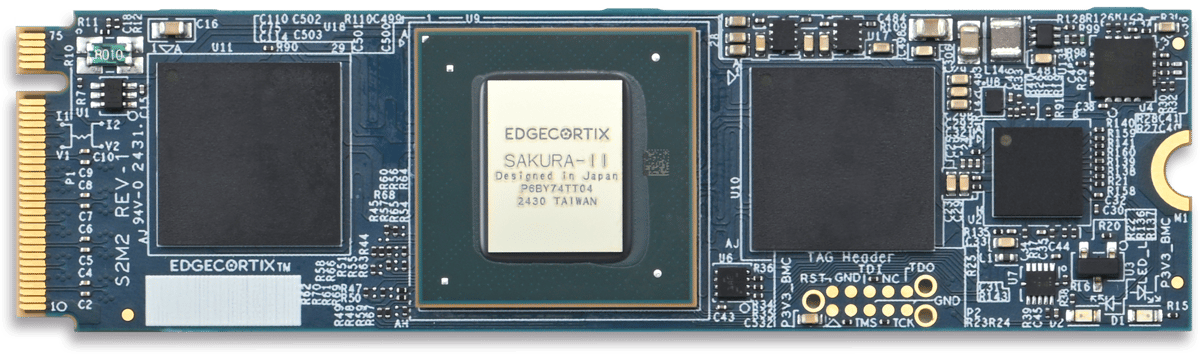

SAKURA-II M.2 Modules and PCIe Cards

EdgeCortix SAKURA-II can be easily integrated into a host system for software development and AI model inference tasks.

Order an M.2 Module or a PCIe Card and get started today!